- Китайские исследователи разработали альтернативную архитектуру DRAM-памяти без отдельного конденсатора.

- Новая ячейка не больше классической, хранит данные дольше и требует более простого техпроцесса.

- Разработка обещает упростить производство оперативной памяти, снизить её стоимость и повысить стабильность работы.

- Ячейка использует схему 2T0C: два управляющих транзистора делят один общий канал хранения.

- Каждая ячейка способна хранить два бита данных - с четырёхуровневым значением заряда.

- Техпроцесс предельно простой: одно экспонирование и одна обработка после него.

- Испытания показали, что ячейка удерживает данные 470-500 секунд без регенерации, что больше, чем у обычной DRAM.

- Задержка чтения составляет около 50 нс - сопоставимо с DDR5.

- Температурный дрейф напряжения затвора остаётся в допустимых пределах.

- Архитектура также подходит для стекового многослойного производства.

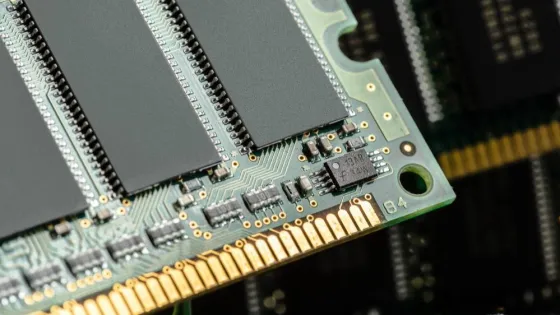

Китай представили новую DRAM без конденсатора — дешевле и проще в производстве

12 янв 2026

Краткий пересказ

от нейросети YandexGPT

Обложка: Изображение из статьи